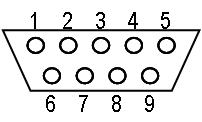

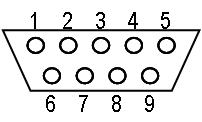

RS232C(正確にはEIA574というらしい)は9-pinコネクタ形状をしている.PC側ではシリアルポートと呼び,COM1とかCOM2がそれにあたる.下に図を示す(オスの場合).

数字はそれぞれピン番号を表す.各ピンの名称等について,下記表に示す.

| ピン | 名称 | 入出力 | 役割 |

| 1 | DCD | in | キャリア検出 |

| 2 | RxD | in | 受信データ |

| 3 | TxD | out | 送信データ |

| 4 | DTR | データ端末レディ | |

| 5 | GND | グラウンド | |

| 6 | DSR | in | データセットレディ |

| 7 | RTS | out | 送信要求 |

| 8 | CTS | in | 送信可能 |

| 9 | RI | 被呼表示 |

入出力のinとかoutは,コネクタを主体として考えた場合.すなわち,RxDには,PCが生成した信号が伝搬する,ということ.逆に,TxDからはFPGAが生成した信号が伝搬し,PC側へと繋がる.ここで,PC側でのRS232C制御は無視(フリーソフトを使う)と,FPGAーPC間の伝送には,RxDとTxDのみ考えればなんとかなる.

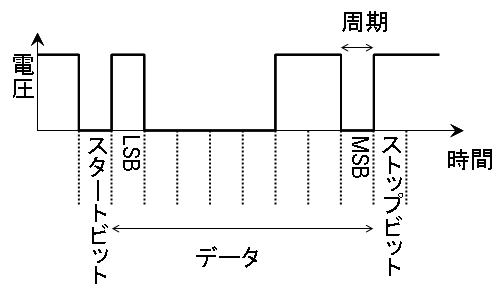

次に,実際にどのような信号が伝達されるのかを説明する.下図は,8bitデータ(10進で97,2進で01100001)・ストップビット1bit・パリティ無しの場合の電気信号である.

まず,RxD/TxD共に,信号を通信していない時は,ある電圧にホールドされている.そして,信号を通信するとき,データをスタートビット"0"とストップビット"1"で挟む.挟まれるデータはLSBから始まり,MSBまで送られる.

このスタート→ストップまでの10bitデータが,ボーレートによって決まる周期で伝搬される.例えば,9600bpsなら1/9600=104.17us間隔で各データが送られる.従って,FPGAでPCから送られたデータを理解するには,まずスタートビットを発見し,続いて8bitデータ分取得する.この際必要となるクロック周期は,当然ボーレートの逆数と等しいかそれ以下である.

では,実際にデータを送る際の信号を生成する方法について述べる.ただし,これから述べることは,「唯一の方法」では無く,「私はこれでできた」ということなので,各人の実行環境に合わせ,適宜修正すること.

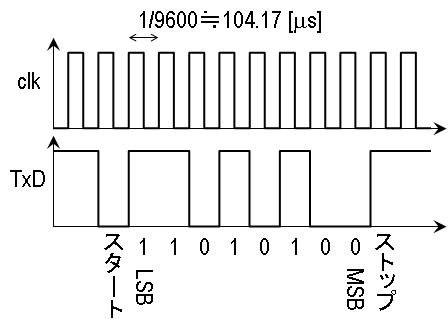

まず,前提として,仕様を以下のように定める.

| 基本クロック周波数 | 100MHz |

| ボーレート | 9600bps |

| 送信データ | 00101011 |

| パリティ | 無し |

| ストップビット | 1bit |

この仕様を満足する電圧波形は,下図のようになる.

ここで,"clk"とは,基本クロックの100MHzから,ボーレートに合わせた分週後のクロックである.このクロック周期にあわせ,送信データTxDを図のようにすれば,受け手側で認識できる.基本クロックから"clk"を生成するには,100e6/9600=10416回をカウントできるカウンタを用意する.2^13<10416<2^14なので,14ビットカウンタで実現できる.

| SEO | [PR] 爆速!無料ブログ 無料ホームページ開設 無料ライブ放送 | ||